46 ISSN 1818-0744

УДК 681.518.3

# Д. С. Потапов, С. В. Верещагин

# Система удаленного реконфигурирования, отладки и тестирования карт электроники для детектора TPC/MPD проекта NICA

Предлагается и рассматривается концепция прототипа устройства на основе интерфейса JTAG, предназначенного для реконфигурирования, отладки и тестирования карт детекторной электроники. Представлены основные составляющие будущего устройства, блок-схемы основных узлов разрабатываемого прототипа. Изложена информация о проекте NICA, детекторе MPD и TPC.

Ключевые слова: мегапроект NICA, TPC, FPGA, JTAG, система удаленного доступа

### Об авторах

**Потапов** Денис Сергеевич — магистрант 1-го курса кафедры проектирования электроники для установок «мегасайенс» Государственного университета «Дубна», инженер научно-экспериментального отдела многоцелевого детектора (*MPD*) Лаборатории физики высоких энергий (ЛФВЭ) Объединенного института ядерных исследований. *E-mail:* potapov-deniska@inbox.ru. 141980. Московская обл., г. Дубна, ул. Академика Балдина 4

**Верещагин Степан Владимирович** – ведущий инженер научно-экспериментального отдела многоцелевого детектора *(MPD)* Лаборатории физики высоких энергий (ЛФВЭ) Объединенного института ядерных исследований.

Новый исследовательский комплекс NICA (Nuclotron based Ion Collider fAcility) нацелен на изучение свойств горячей и плотной барионной материи при столкновении тяжелых ионов (вплоть до  $\mathrm{Au}^{79+}$ ) в диапазоне энергий в системе центра масс  $4 < \sqrt{S_{NN}} < 11$  ГэВ при средней светимости  $L=10^{27}$  см $^{-2}$  с $^{-1}$  [3]. Многоцелевой детектор (Multi-Purpose Detector, MPD) будет располагаться в одной из двух точек пересечения пучков и оптимизирован для исследований соударений тяжелых ионов [2].

Время-проекционная камера (Time Projection Chamber, TPC) является главным трековым детектором в МРО [7]. ТРС будет помещена в центре MPD и обеспечит регистрацию треков (до 2000 при центральном столкновении) от заряженных частиц при частоте событий в 7 кГц и позволит идентифицировать эти частицы. Регистрация зарядов от треков в ТРС будет осуществляться 24 считывающими камерами (Read Out Chamber, ROC камера), реализуемыми по технологии многопроволочных пропорциональных камер с катодным пэдовым считыванием, которые будут расположены на ее торцах.

Система сбора данных с одной ROC камеры включает в себя 62 карты считывания (Front-End Card, FEC). Общее количество карт

FEC на всей TPC составит 1488 штук. Карты FEC будут расположены на ROC камере вне чувствительной области детектора. Карта FEC состоит из двух частей: карты усиления сигнала и оцифровки его формы и интерфейсной контроллерной карты [6; 7]. В качестве ядра интерфейсной карты используется ПЛИС (Field-Programmable Gate Array, FPGA) Cyclone V [1] с поддержкой JTAG-интерфейса [4].

# Система удаленного реконфигурирования и отладки карт детекторной электроники

По причине недоступности детекторной электроники в течение эксперимента и предъявляемым высоким требованиям к надежности системы сбора данных было принято решение о разработке устройства, обеспечивающего удаленный доступ к ПЛИС каждой из 62 карт FEC, расположенных на каждой ROC камере. Проектируемое устройство будет использовать интерфейс JTAG, имеющийся на каждой плате и используемый для перепрограммирования ПЛИС, отладки цифровой логики, а также обеспечивающий дополнительный медленный канал управления картами FEC.

Для доступа к функционалу, обеспечиваемому интерфейсом JTAG на карте FEC, используется фирменный программатор, который имеет возможность единовременного доступа лишь к одной карте. Разрабатываемое устройство будет являться коммутатором, ко-

торый расширит функционал программатора до возможности обслуживания семи карт FEC в прототипе устройства и 62 карт FEC в конечном исполнении.

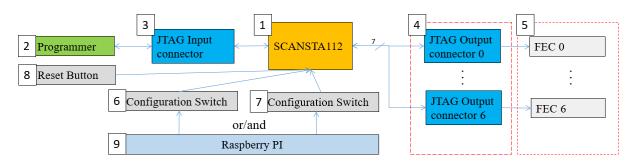

В качестве главного компонента разрабатываемого прототипа устройства используется микросхема SCANSTA112 [5], представляющая семипортовый мультиплексор аппаратного интерфейса на базе стандарта IEEE 1149.1 (JTAG). Использование микросхемы SCANSTA112 позволяет изолировать JTAGклиентов друг от друга и не использовать сложные цепочки сканирования, что полезно для работы с ПЛИС. На рис. 1 представлена блок-схема разрабатываемого прототипа устройства.

Фирменный программатор (рис. 1 п. 2) будет подключаться к входному JTAG порту (рис. 1 п. 3, рис. 2 п.1). Система выходных (локальных) JTAG портов 0–6 (рис. 1 п. 4, рис. 2 п. 3) будут связаны с интерфейсной частью карты FEC (рис. 1 п. 5) для реконфигурирования и отладки. Разъемы входных и выходных портов будут распложены на печатной плате разрабатываемого устройства.

Для управления режимами работы микросхемы SCANSTA112 будет использовано два конфигурационных переключателя. Первый переключатель, однобитный (рис. 1 п. 6), будет использоваться для управления входом  $SB/\bar{S}$  (рис. 2 п. 5), выбирающим режим работы коммутатора. Значение равное «0» соответствует режиму работы Stitcher Mode, значение равное «1» соответствует режиму работы ScanBridge Mode. Второй, семибитный переключатель (рис. 1 п. 7), будет задействован в режиме работы Stitcher Mode. С помощью этого переключателя будет производиться выбор локальных портов ЈТАС, установкой соответствующих уровней на входах  $LSPSel_{0-6}$ (рис. 2 п. 4). Кнопка сброса (Reset Button, рис. 1 п. 8) будет использоваться для сброса заданных настроек мультиплексора при изменении значений на конфигурационных входах.

На втором этапе управление значениями конфигурационных входов будет осуществляться через одноплатный компьютер "Raspberry PI" (рис. 1 п. 9). Внедрение в систему "Raspberry PI" повысит степень автоматизации этой системы и обеспечит возможность удаленного управления устройством.

Рис. 1. Блок-схема разрабатываемого прототипа устройства:

1 — микросхема SCANSTA112; 2 — программатор; 3 — входной разъем JTAG; 4 — выходные разъемы JTAG порты; 5 — карты FEC; 6 — однобитный переключатель; 7 — семибитный переключатель; 8 — кнопка сброса; 9 — одноплатный компьютер "Raspberry PI"

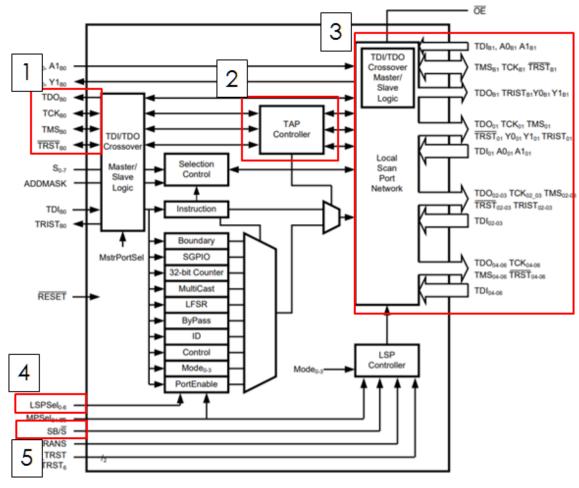

В качестве ядра и центрального управления мультиплексором SCANSTA112 выступает TAP controller (рис. 2 п. 2) – конечный автомат на 16 состояний. Контроль интерфейса JTAG выполняется управляющим сигналом

TMS, влияющим на состояние автомата. Управление осуществляется по переднему фронту сигнала СLК. Чтение и запись данных происходят одновременно. На рис. 2 приведены основные узлы ядра мультиплексора.

48 ISSN 1818-0744

Рис. 2. Блок-схема мультиплексора SCANSTA112:

I — входной JTAG интерфейс; 2 — TAP controller; 3 — система локальных (выходных) портов JTAG (семь штук); 4 — управляющие входы  $LSPSel_{0-6}$ ; 5 — управляющий вход  $SB/\bar{S}$ .

Разрабатываемый прототип устройства обеспечит возможность доступа ко всему функционалу, предоставляемому интерфейсом JTAG, на любой из семи подключенных платах FEC с использованием всего одного программатора.

Мультиплексор SCANSTA112 имеет два режима работы:

- 1. Stitcher Mode В этом режиме возможна работа только с одним мультиплексором SCANSTA112. Преимущества режима в его простоте в связи с отсутствием двухуровневого управляющего протокола. В данном режиме выбор локального JTAG порта осуществляется заданием значения на соответствующих конфигурационных входах, после чего мультиплексор SCANSTA112 сразу готов к работе. Недостаток Stitcher Mode в его меньшей гибкости в сравнении со вторым режимом работы.

- 2. ScanBridge Mode. В этом режиме можно работать как с одним, так и с несколь-

кими мультиплексорами SCANSTA112. Преимущества заключаются в том, что режим имеет дополнительный функционал и обладает большей гибкостью. Недостатки — этот режим более сложный в реализации и использовании, оснащен дополнительным двухуровневым управляющим протоколом.

Для начального этапа работы с прототипом разрабатываемого устройства, на основе одного мультиплексора SCANSTA112, выбран режим Stitcher Mode.

Для реализации системы для одной камеры, состоящей из 62 карт FEC, существуют два пути:

- 1) работать в режиме ScanBridge Mode, соединяя мультиплексоры SCANSTA112 в шину;

- 2) каскадировать мультиплексоры SCANSTA112.

#### Заключение

В работе рассмотрена и представлена концепция прототипа устройства способного обеспечить возможность доступа ко всему функционалу, предоставляемому интерфейсом JTAG, на любой из семи подключенных платах FEC с использованием всего одного программатора. Приведена и описана блок-схема прототипа, изложен принцип ее работы. Рассказано об основных узлах мультиплексора SCANSTA112 и определен режим его работы для начального этапа. В данный момент проект находится на стадии разработки электрической принципиальной схемы прототипа устройства.

## Библиографический список

- 1. Altera Corporation, Cyclone V Device Handbook, 2020. [Электронный ресурс]. URL: https://www.intel.com/content/dam/www/programmab le/us/en/pdfs/literature/hb/ cyclone -v/cv\_5v2.pdf (дата обращения: 01.12.2020).

- 2. Geraksiev N. The nuclotron-based ion collider facility project. The physics programme for the

- multi-purpose detector // J. Phys. Conf. Ser. 1390. 2019. P. 012121.

- 3. Kekelidze V. NICA project at JINR: status and prospects // JINST. 2017. № 12. P. 06012.

- 4. Texas Instruments, IEEE Std 1149.1 (JTAG) Testability, 1997. [Электронный ресурс]. URL: https://www.ti.com/lit/an/ssya002c/ssya002c.pdf (дата обращения: 01.12.2020).

- 5. Texas Instruments, SCANSTA112 7-Port Multidrop IEEE 1149.1 (JTAG) Multiplexer, 2013. [Электронный ресурс]. URL: https://www.ti.com/lit/ds/symlink/scansta

- 112.pdf?ts=1608836747286&ref\_url=https%253A%2 52F%252Fwww.ti.com%252Fproduct%252FSCANST A112 (дата обращения: 01.12.2020).

- 6. Vereschagin S., Movchan S., and Zaporozhets S. Front-end electronics development for TPC/MPD detector of NICA project // JINST. 2020. N 15. P. C09044.

- 7. Vereschagin S., Bazhazhin A., Fateev O., Lukstins J., Movchan S., Razin S., Zaporozhets S., Zruev V., Time-projection chamber for multi-purpose detector of NICA project at JINR // Nucl. Instrum. Meth. A 958. 2020. 162793.

Поступила в редакцию 27.11.2020